## SuperH<sup>TM</sup> (SH) 64-Bit RISC Series

# SH-5 System Architecture, Volume 1: System

Last updated 18 March 2002

#### SuperH, Inc.

This publication contains proprietary information of SuperH, Inc., and is not to be copied in whole or part.

Issued by the SuperH Documentation Group on behalf of SuperH, Inc.

Information furnished is believed to be accurate and reliable. However, SuperH, Inc. assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SuperH, Inc. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SuperH, Inc. products are not authorized for use as critical components in life support devices or systems without the express written approval of SuperH, Inc.

is a registered trademark of SuperH, Inc.

SuperH is a registered trademark for products originally developed by Hitachi, Ltd. and is owned by Hitachi Ltd.

© 2001, 2002 SuperH, Inc. All Rights Reserved.

SuperH, Inc. San Jose, U.S.A. - Bristol, United Kingdom - Tokyo, Japan

www.superh.com

#### PRELIMINARY DATA

### **Contents**

|   | Pre | eface                        | xi |

|---|-----|------------------------------|----|

| 1 | Ove | erview                       | 1  |

|   | 1.1 | Introduction                 | 1  |

|   |     | 1.1.1 Address map            | 4  |

|   |     | 1.1.2 Interrupt architecture | 4  |

|   |     | 1.1.3 DMA architecture       | 4  |

|   | 1.2 | Debug architecture           | 5  |

| 2 | Sys | tem organization             | 9  |

|   | 2.1 | Introduction                 | 9  |

|   | 2.2 | SuperHyway architecture      | 9  |

|   |     | 2.2.1 Packets                | 11 |

|   |     | 2.2.2 Transactions           | 12 |

|   |     | 2.2.3 Packet-router          | 14 |

|   |     | 2.2.4 SuperHyway ports       | 15 |

|   |     | 2.2.5 SH-5 modules           | 15 |

|   |     | 2.2.6 SuperHyway protocol    | 16 |

| 2.3 | Cache  | coherency support                                    | 19 |

|-----|--------|------------------------------------------------------|----|

|     | 2.3.1  | Flush                                                | 19 |

|     | 2.3.2  | Purge                                                | 20 |

|     | 2.3.3  | Coherency maintenance                                | 20 |

|     | 2.3.4  | Use of coherency transactions                        | 21 |

| 2.4 | Other  | features                                             | 21 |

|     | 2.4.1  | Module powerdown                                     | 21 |

|     | 2.4.2  | Debug features                                       | 22 |

| 2.5 | SH-5   | SuperHyway implementation                            | 22 |

|     | 2.5.1  | Supported transactions                               | 23 |

|     | 2.5.2  | Implementation                                       | 23 |

|     | 2.5.3  | Data organization                                    | 24 |

|     | 2.5.4  | SH-5 physical memory organization                    | 25 |

| 2.6 | SH-5 ] | physical address map                                 | 26 |

|     | 2.6.1  | SH-5 debug link                                      | 29 |

| 2.7 | SH-5   | conventions                                          | 29 |

|     | 2.7.1  | Memory blocks                                        | 29 |

|     | 2.7.2  | Control registers                                    | 30 |

|     | 2.7.3  | Version control registers                            | 34 |

|     | 2.7.4  | P-error flags                                        | 37 |

|     | 2.7.5  | M-error flags                                        | 41 |

|     | 2.7.6  | Memory map conventions                               | 41 |

|     | 2.7.7  | P-module specification standards                     | 42 |

| 2.8 | SH-5   | endianess and data mapping                           | 43 |

|     | 2.8.1  | Accessing memory                                     | 43 |

|     | 2.8.2  | Accessing device registers                           | 43 |

|     | 2.8.3  | Accessing PCI memory space                           | 44 |

|     | 2.8.4  | Using the SHdebug link                               | 44 |

|     | 2.8.5  | SuperHyway byte lane mapping                         | 44 |

| 2.9 | SH-5   | undefined behavior                                   | 47 |

|     | 2.9.1  | SH-5 chip-level architecturally undefined behavior   | 47 |

|     | 2.9.2  | SH-5 module-level architecturally undefined behavior | 48 |

|     | 2.9.3  | Unresponsive modules                                 | 50 |

| 3 | SH-5 CPU |       |                                |    |  |

|---|----------|-------|--------------------------------|----|--|

|   | 3.1      | Intro | duction                        | 53 |  |

|   | 3.2      | CPU   | port                           | 53 |  |

|   |          | 3.2.1 | Instruction fetch              | 53 |  |

|   |          | 3.2.2 | Data access                    | 54 |  |

|   | 3.3      | Cache | e coherency support            | 55 |  |

|   |          | 3.3.1 | Operand cache snooping         | 55 |  |

|   |          | 3.3.2 | Flush                          | 55 |  |

|   |          | 3.3.3 | Purge                          | 56 |  |

|   |          | 3.3.4 | Coherency maintenance          | 57 |  |

|   |          | 3.3.5 | Cache controller behaviour     | 57 |  |

|   |          | 3.3.6 | Use of coherency transactions  | 58 |  |

|   | 3.4      | Bi-en | dian support                   | 58 |  |

|   | 3.5      | Memo  | ory mapped registers           | 59 |  |

|   |          | 3.5.1 | CPU.VCR                        | 59 |  |

| 4 | DM       | A con | troller                        | 63 |  |

|   | 4.1      | Featu | ares                           | 63 |  |

|   | 4.2      | Addre | ess map                        | 64 |  |

|   | 4.3      | Opera | ation                          | 65 |  |

|   |          | 4.3.1 | DMA basic transfer procedure   | 65 |  |

|   |          | 4.3.2 | Configuring a DMA channel      | 66 |  |

|   |          | 4.3.3 | Errors and suspended channels  | 66 |  |

|   |          | 4.3.4 | DMA channel completion status  | 68 |  |

|   |          | 4.3.5 | Request modes                  | 68 |  |

|   |          | 4.3.6 | Channel priorities             | 69 |  |

|   |          | 4.3.7 | Interrupts                     | 70 |  |

|   |          | 4.3.8 | Behavior of SAR, DAR and count | 71 |  |

|   | 4.4  | Regis | ter descriptions                 | 73  |

|---|------|-------|----------------------------------|-----|

|   |      | 4.4.1 | DMAC.VCR                         | 73  |

|   |      | 4.4.2 | DMAC.COMMON                      | 77  |

|   |      | 4.4.3 | DMAC.SAR[n]                      | 80  |

|   |      | 4.4.4 | DMAC.DAR[n]                      | 81  |

|   |      | 4.4.5 | DMAC.COUNT[n]                    | 82  |

|   |      | 4.4.6 | DMAC.CTRL[n]                     | 83  |

|   |      | 4.4.7 | DMAC.STATUS[n]                   | 86  |

|   |      | 4.4.8 | DMA external pin control (DMAEX) | 87  |

|   | 4.5  | DMA   | C SuperHyway transactions        | 91  |

|   |      | 4.5.1 | DMAC as a request target         | 91  |

|   |      | 4.5.2 | DMAC as a request initiator      | 91  |

|   | 4.6  | Powe  | r down                           | 92  |

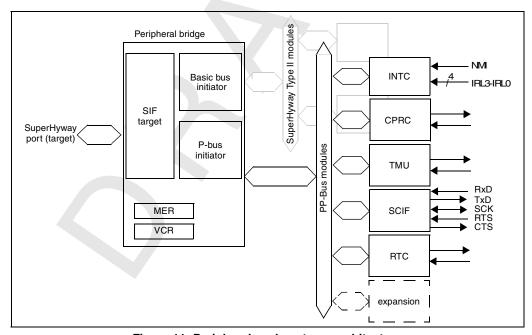

| 5 | Per  | ipher | al bridge                        | 93  |

|   | 5.1  | Intro | duction                          | 93  |

|   | 5.2  | Funct | tionality                        | 94  |

|   |      | 5.2.1 | Overview                         | 94  |

|   |      | 5.2.2 | Address map                      | 95  |

|   | 5.3  | Opera | ation                            | 96  |

|   |      | 5.3.1 | Bridge registers                 | 96  |

|   |      | 5.3.2 | SuperHyway type 2 area           | 96  |

|   |      | 5.3.3 | PP-Bus area                      | 97  |

|   |      | 5.3.4 | Peripheral bridge registers      | 99  |

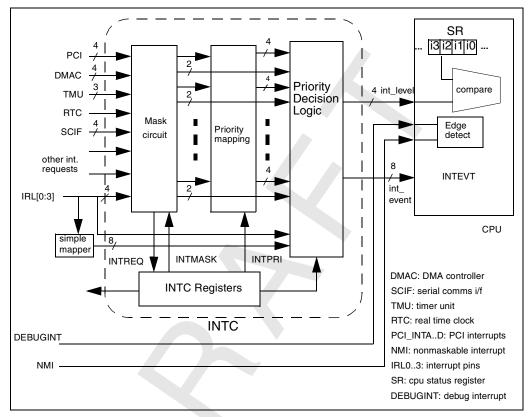

| 6 | Inte | errup | t controller                     | 107 |

|   | 6.1  | Featu | ures                             | 107 |

|   |      | 6.1.1 | Block diagram                    | 108 |

|   |      | 6.1.2 | Pin configuration                | 109 |

|   |      | 6.1.3 | Register configuration           | 109 |

|   | 6.2 | Interr  | rupt sources                           | 110 |

|---|-----|---------|----------------------------------------|-----|

|   |     | 6.2.1   | NMI interrupts                         | 111 |

|   |     | 6.2.2   | IRL interrupts                         | 111 |

|   |     | 6.2.3   | On-chip peripheral module interrupts   | 114 |

|   |     | 6.2.4   | Reserved interrupts                    | 114 |

|   |     | 6.2.5   | DEBUG interrupt                        | 114 |

|   | 6.3 | Interr  | rupt exception handling and priority   | 115 |

|   |     | 6.3.1   | Interrupt masking                      | 118 |

|   | 6.4 | Regist  | ter descriptions                       | 119 |

|   |     | 6.4.1   | INTC operation                         | 134 |

|   |     | 6.4.2   | Transactions                           | 135 |

| 7 | Rea | ıl-time | e clock (RTC)                          | 137 |

|   | 7.1 | Overv   | riew                                   | 137 |

|   |     | 7.1.1   | Features                               | 137 |

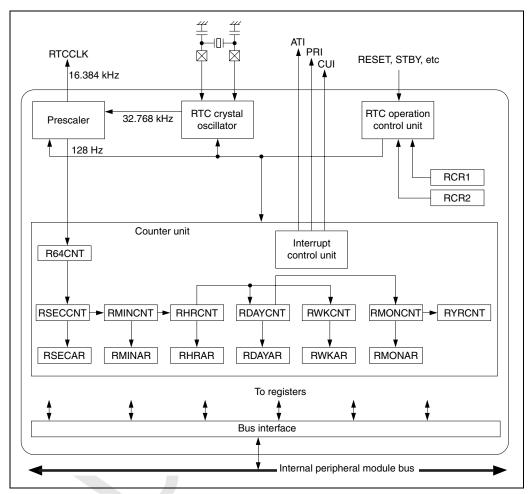

|   |     | 7.1.2   | Block diagram                          | 138 |

|   |     | 7.1.3   | Pin configuration                      | 139 |

|   |     | 7.1.4   | Register configuration                 | 139 |

|   | 7.2 | Regist  | ter descriptions                       | 141 |

|   |     | 7.2.1   | Frequency divider counter (RTC.R64CNT) | 141 |

|   |     | 7.2.2   | Second counter (RTC.RSECCNT)           | 142 |

|   |     | 7.2.3   | Minute counter (RTC.RMINCNT)           | 144 |

|   |     | 7.2.4   | Hour counter (RTC.RHRCNT)              | 145 |

|   |     | 7.2.5   | Day-of-week counter (RTC.RWKCNT)       | 146 |

|   |     | 7.2.6   | Day counter (RTC.RDAYCNT)              | 147 |

|   |     | 7.2.7   | Month counter (RTC.RMONCNT)            | 148 |

|   |     | 7.2.8   | Year counter (RTC.RYRCNT)              | 149 |

|   |     | 7.2.9   | Second alarm register (RTC.RSECAR)     | 151 |

|   |     | 7.2.10  | Minute alarm register (RTC.RMINAR)     | 152 |

|   |     | 7.2.11  | Hour alarm register (RTC.RHRAR)        | 153 |

|   |     | 7.2.12  | Day-of-week alarm register (RTC.RWKAR) | 155 |

|   |     | 7213    | Day alarm register (RTC RDAYAR)        | 156 |

|   |                | 7.2.14 | Month alarm register (RTC.RMONAR)        | 158 |

|---|----------------|--------|------------------------------------------|-----|

|   |                | 7.2.15 | RTC control register 1 (RTC.RCR1)        | 160 |

|   |                | 7.2.16 | RTC control register 2 (RTC.RCR2)        | 163 |

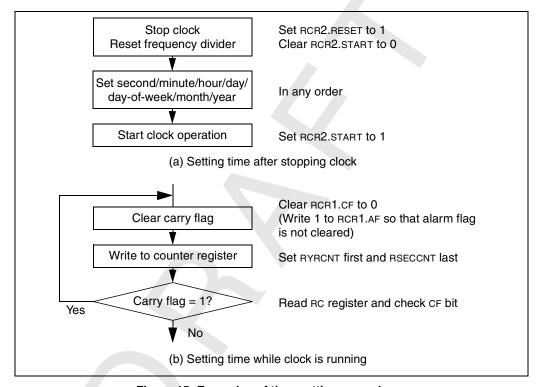

|   | 7.3            | Opera  | tion                                     | 166 |

|   |                | 7.3.1  | Time setting procedures                  | 166 |

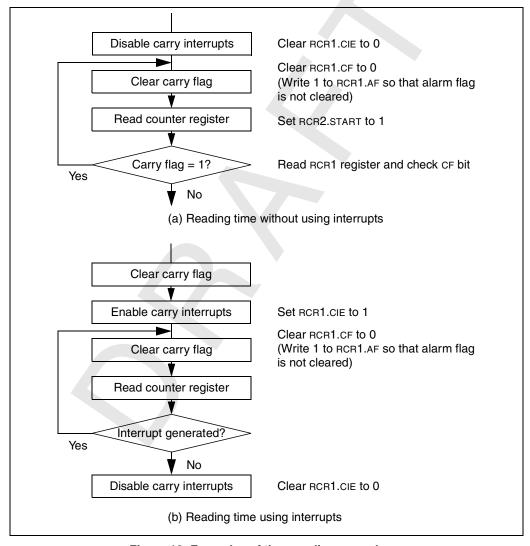

|   |                | 7.3.2  | Time reading procedures                  | 167 |

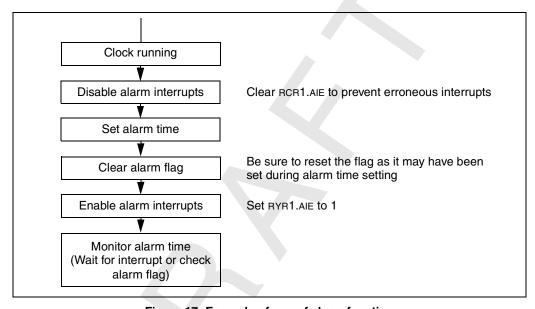

|   |                | 7.3.3  | Alarm function                           | 168 |

|   | 7.4            | Interr | upts                                     | 169 |

|   | 7.5            | Usage  | notes                                    | 169 |

|   |                | 7.5.1  | Register initialization                  | 169 |

|   |                | 7.5.2  | Crystal oscillator circuit               | 169 |

| 8 | Tim            | or un  | it (TMU)                                 | 171 |

| O | 1 1111         | er um  | it (IWO)                                 | 111 |

|   | 8.1            | Overv  | iew                                      | 171 |

|   |                | 8.1.1  | Features                                 | 171 |

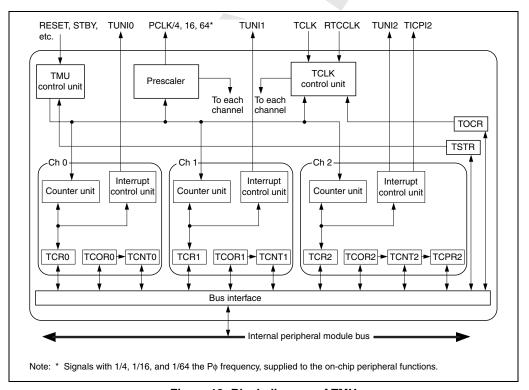

|   |                | 8.1.2  | Block diagram                            | 172 |

|   |                | 8.1.3  | Pin configuration                        | 173 |

|   |                | 8.1.4  | Register configuration                   | 173 |

|   | 8.2            | Regist | er descriptions                          | 175 |

|   |                | 8.2.1  | Timer output control register (TMU.TOCR) | 175 |

|   |                | 8.2.2  | Timer start register (TMU.TSTR)          | 176 |

|   |                | 8.2.3  | Timer constant registers (TMU.TCOR)      | 178 |

|   |                | 8.2.4  | Timer Counters (TMU.TCNT)                | 178 |

|   |                | 8.2.5  | Timer control registers (TMU.TCR)        | 179 |

|   |                | 8.2.6  | Input capture register (TMU.TCPR2)       | 185 |

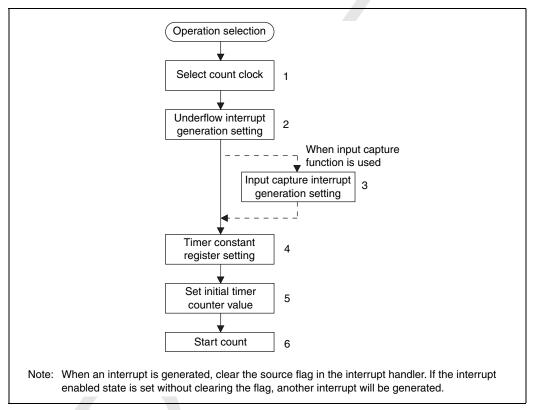

|   | 8.3            | Opera  | tion                                     | 186 |

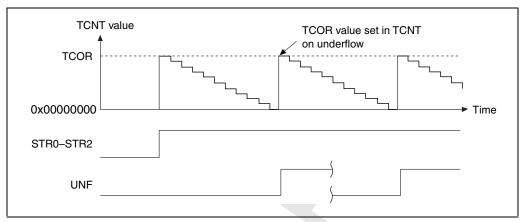

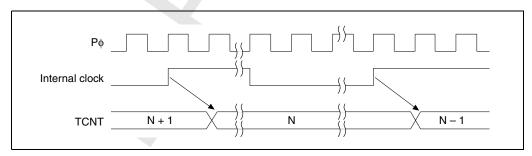

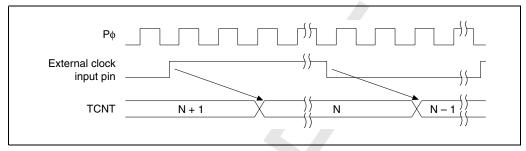

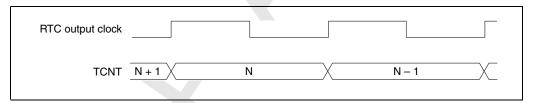

|   |                | 8.3.1  | Counter operation                        | 186 |

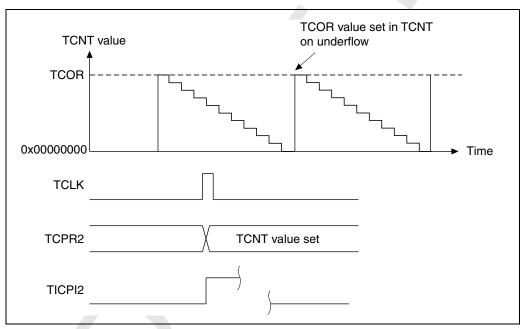

|   |                | 8.3.2  | Input capture function                   | 189 |

|   | 8.4 Interrupts |        |                                          | 191 |

|   | 8.5 | Usage   | e notes                                    | 192 |

|---|-----|---------|--------------------------------------------|-----|

|   |     | 8.5.1   | Register writes                            | 192 |

|   |     | 8.5.2   | TCNT register reads                        | 192 |

|   |     | 8.5.3   | Resetting the RTC frequency divider        | 192 |

|   |     | 8.5.4   | External clock frequency                   | 192 |

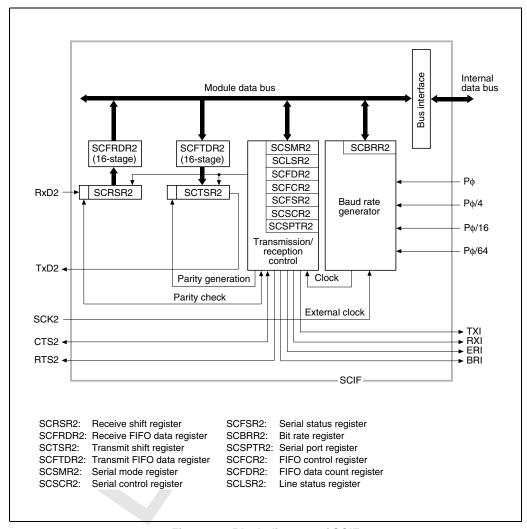

| 9 | Ser | ial cor | mms interface with FIFO (SCIF)             | 193 |

|   | 9.1 | Overv   | riew                                       | 193 |

|   |     | 9.1.1   | Features                                   | 193 |

|   |     | 9.1.2   | Block diagram                              | 195 |

|   |     | 9.1.3   | Pin configuration                          | 196 |

|   |     | 9.1.4   | Register configuration                     | 196 |

|   | 9.2 | Regist  | ter descriptions                           | 197 |

|   |     | 9.2.1   | Receive shift register (SCIF.SCRSR2)       | 197 |

|   |     | 9.2.2   | Receive FIFO data register (SCIF.SCFRDR2)  | 198 |

|   |     | 9.2.3   | Transmit shift register (SCIF.SCTSR2)      | 198 |

|   |     | 9.2.4   | Transmit FIFO data register (SCIF.SCFTDR2) | 199 |

|   |     | 9.2.5   | Serial mode register (SCIF.SCSMR2)         | 200 |

|   |     | 9.2.6   | Serial control register (SCIF.SCSCR2)      | 204 |

|   |     | 9.2.7   | Serial status register (SCIF.SCFSR2)       | 210 |

|   |     | 9.2.8   | Bit rate register (SCIF.SCBRR2)            | 221 |

|   |     | 9.2.9   | FIFO control register (SCIF.SCFCR2)        | 223 |

|   |     | 9.2.10  | FIFO data count register (SCIF.SCFDR2)     | 229 |

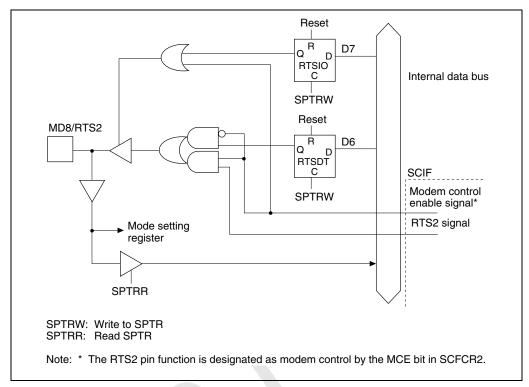

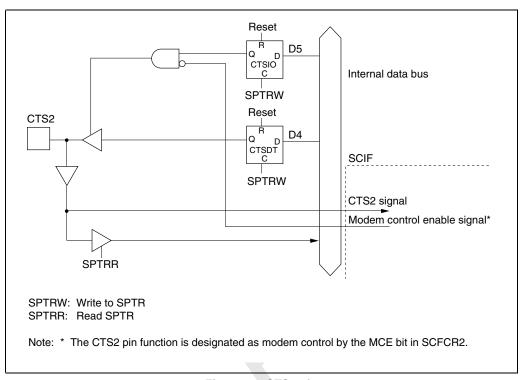

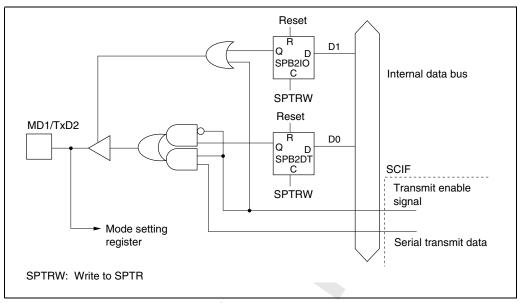

|   |     | 9.2.11  | Serial port register (SCIF.SCSPTR2)        | 231 |

|   |     | 9.2.12  | Line status register (SCIF.SCLSR2)         | 240 |

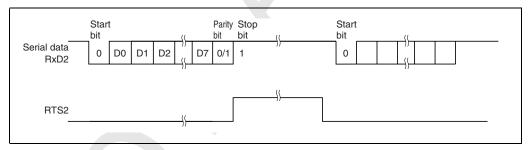

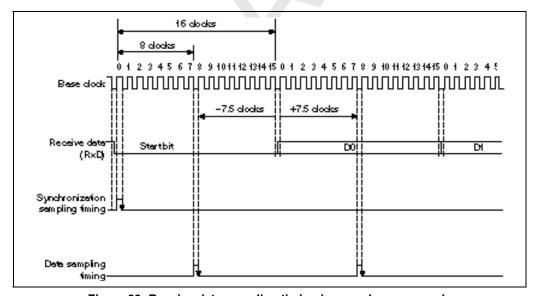

|   | 9.3 | Opera   | ation                                      | 241 |

|   |     | 9.3.1   | Overview                                   | 241 |

|   |     | 9.3.2   | Serial operation                           | 243 |

|   | 9.4 | SCIF    | interrupt sources and the DMAC             | 254 |

|   | 9.5 | Power   | c down                                     | 255 |

|   | 9.6 | Usage   | e notes                                    | 256 |

| 10 | Clock, power and reset controller |         |                                           |     |  |

|----|-----------------------------------|---------|-------------------------------------------|-----|--|

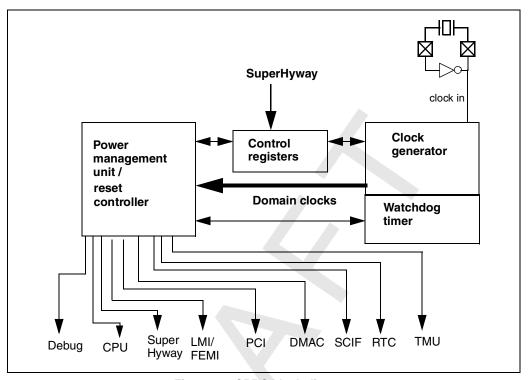

|    | 10.1                              | Overvi  | iew                                       | 259 |  |

|    |                                   | 10.1.1  | Features                                  | 260 |  |

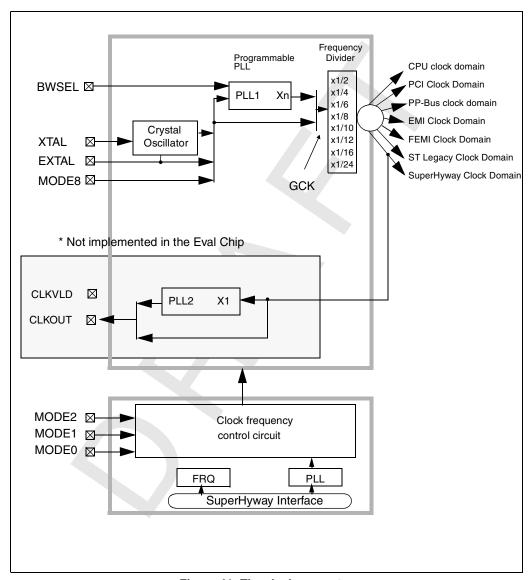

|    | 10.2                              | Clock   | pulse generator (CPG)                     | 261 |  |

|    |                                   | 10.2.1  | CPG pin configuration                     | 263 |  |

|    |                                   | 10.2.2  | CPG register configuration                | 264 |  |

|    |                                   | 10.2.3  | Clock operating modes                     | 264 |  |

|    |                                   | 10.2.4  | Clock domains                             | 266 |  |

|    |                                   | 10.2.5  | Control registers                         | 267 |  |

|    |                                   | 10.2.6  | Configuring PLL1                          | 275 |  |

|    |                                   | 10.2.7  | Changing the frequency                    | 276 |  |

|    |                                   | 10.2.8  | Output clock control                      | 278 |  |

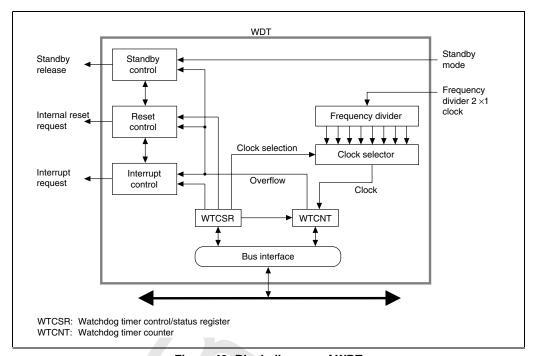

|    | 10.3                              | Watch   | dog timer                                 | 279 |  |

|    |                                   | 10.3.1  | Register configuration                    | 280 |  |

|    |                                   | 10.3.2  | WDT register descriptions                 | 280 |  |

|    |                                   | 10.3.3  | Using the WDT                             | 285 |  |

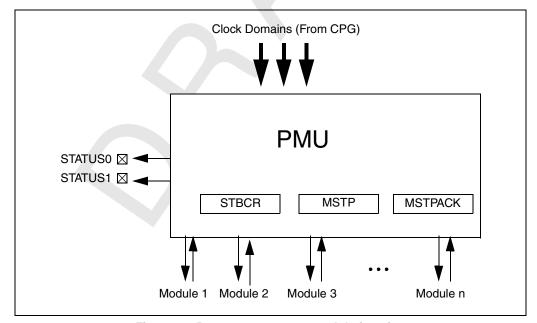

|    | 10.4                              | Power   | management unit (PMU)                     | 287 |  |

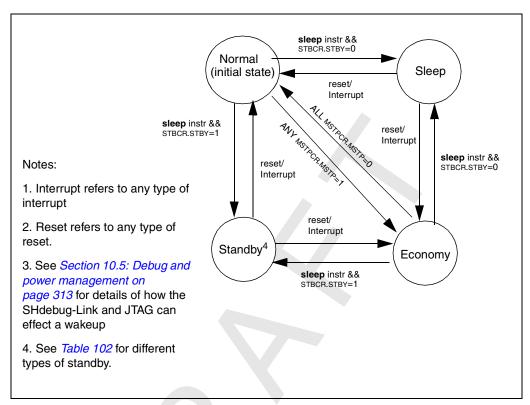

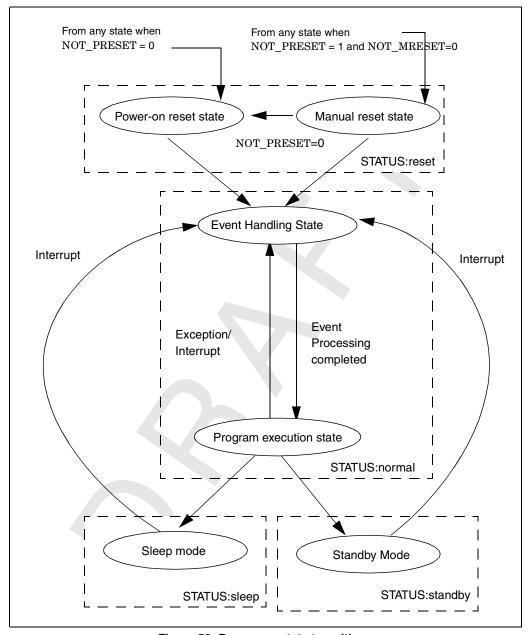

|    |                                   | 10.4.1  | Types of power modes                      | 288 |  |

|    |                                   | 10.4.2  | Register configuration                    | 290 |  |

|    |                                   | 10.4.3  | Pin configuration                         | 290 |  |

|    |                                   | 10.4.4  | Overview                                  | 291 |  |

|    |                                   | 10.4.5  | Register descriptions                     | 292 |  |

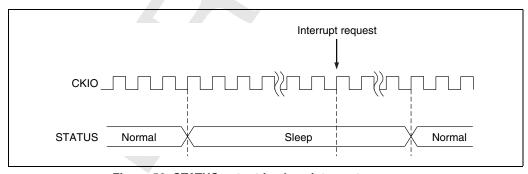

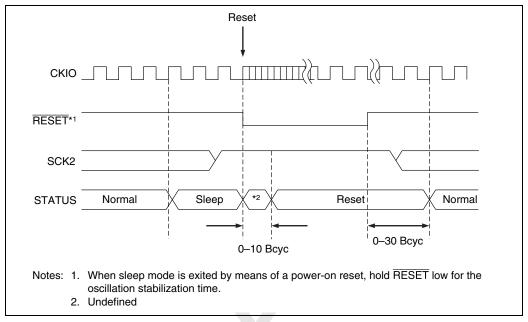

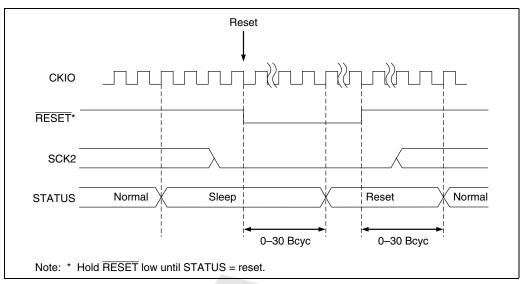

|    |                                   | 10.4.6  | Sleep mode                                | 302 |  |

|    |                                   | 10.4.7  | Standby mode                              | 303 |  |

|    |                                   | 10.4.8  | Exit from standby mode                    | 305 |  |

|    |                                   | 10.4.9  | Clock pause function                      | 306 |  |

|    |                                   | 10.4.10 | Economy mode                              | 307 |  |

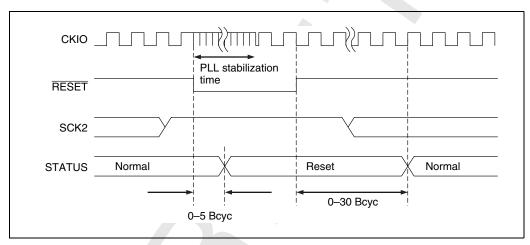

|    |                                   | 10.4.11 | STATUS pin change timing                  | 307 |  |

|    | 10.5                              | Debug   | and power management                      | 313 |  |

|    |                                   | 10.5.1  | Debug enable/disable                      | 313 |  |

|    |                                   | 10.5.2  | Debug module state with no tool connected | 314 |  |

|    |                                   | 10.5.3  | Debug wakeup from standby state           | 314 |  |

|    |                                   | 10 5 4  | Debug wakeun from sleen states            | 315 |  |

| 10.6 | Reset  | controller                                 | 316 |

|------|--------|--------------------------------------------|-----|

|      | 10.6.1 | Reset pins                                 | 318 |

|      | 10.6.2 | Reset function                             | 319 |

|      | 10.6.3 | Reset functions available from debug tools | 320 |

|      | 10.6.4 | Reset status                               | 320 |

|      | 10.6.5 | Register summary                           | 321 |

|      |        |                                            |     |

| Inde | ex     |                                            | 323 |

5

### **Preface**

This document is part of the SuperH SH-5 CPU system documentation suite detailed below. Comments on this or other books in the documentation suite should be made by contacting your local sales office or distributor.

## **SuperH SH-5 document identification and control**

Each book in the documentation suite carries a unique identifier in the form:

05-SA-nnnn Vx.x

Where, n is the document number and x.x is the revision.

Whenever making comments on a SuperH SH-5 document the complete identification 05-SA-1000n Vx.x should be quoted.

## **SuperH SH-5 system architecture documentation suite**

The SuperH SH-5 system architecture documentation suite comprises the following volumes:

- SH-5 System Architecture, Volume 1: System (05-SA-10001)

- SH-5 System Architecture, Volume 2: Peripherals (05-SA-10002)

- SH-5 System Architecture, Volume 3: Debug (05-SA-10003)

## 1

### **Overview**

#### 1.1 Introduction

The SH-5 architecture forms the common centre of a family of products. This document describes the infrastructure built to support the development of this family. To aid in this description, the STB1 evaluation device is used as an example. This device is a technology demonstrator enabling product focused systems to be developed rapidly.

| Eval chip features                                                         |                                                                              |  |  |  |  |  |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| SH-5 RISC CPU                                                              | Flash/ROM interface                                                          |  |  |  |  |  |

| Single-issue 64-bit core                                                   | 8/16/32-bit data, 26-bit address                                             |  |  |  |  |  |

| 400 MHz internal clock speed                                               | Write cycle for flash memory support                                         |  |  |  |  |  |

| On-chip separate i&d caches and TLB's                                      | Wait pin for slow devices                                                    |  |  |  |  |  |

| PCI interface                                                              | Five decoded CS_N signals                                                    |  |  |  |  |  |

| PCI 2.1, 32-bit, 66 MHz                                                    | Target part: Intel flash P/N: 28F032SA                                       |  |  |  |  |  |

| Support bus mastering to main memory with multiple pipe-lined transactions | LVTTL I/O                                                                    |  |  |  |  |  |

| Support four external bus masters                                          | DMA controller                                                               |  |  |  |  |  |

| PCI to system memory is cache coherent                                     | Four channels                                                                |  |  |  |  |  |

| Support configuration as PCI peripheral (non-host)                         | Clock controller with S/W programmable ratios for internal / external clocks |  |  |  |  |  |

| 3.3 V PCI                                                                  |                                                                              |  |  |  |  |  |

**Table 1: Features**

#### **Eval chip features**

#### SDRAM interface SDR/DDR

32/64-bit, 133 MHz, 64 Mbyte, 256 Mbyte

Support four open banks

Support both PC100 and 133 MHz DDR SDRAM

Support power saving idle / standby states

Target parts: Hitachi P/N: 54S64XXD2 & Intel PC100 SDRAM standard

#### Multiple timers

32-bit timer with auto reload, interrupts

Configurable input clocks

#### Real time clock

On-chip oscillator circuit

Built-in clock, calendar, alarm, IRQ

#### Interrupt controller

Configurable priorities

Internal peripheral interrupts

#### Debug support

High speed debug interface (100 MHz), independent of JTAG

Development host can access entire internal address space, non-intrusively

CPU can boot from debug adapter interface

CPU core has code address, operand and opcode watchpoints plus branch trace and fast printf functions

Watchpoints and trace on internal bus (SuperHyway)

All watchpoints can send trace packets to debug link (non-intrusively) or generate CPU debug trap

Performance counters for CPU core and bus parameters

#### SCIF

UART FIFO serial interface with DMA

16 byte FIFO

S/W configured baud clock generator

#### Power management unit

Control unit and peripheral power saving modes

Watchdog timer fuction (reset hard and soft)

**Table 1: Features**

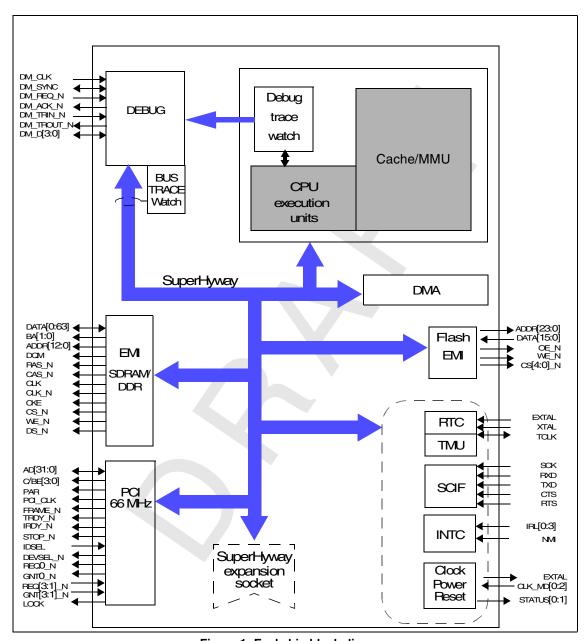

Figure 1: Eval chip block diagram

3

The organization of interconnects in the system illustrated in *Figure 1* is guided by the principle of optimizing each interconnect for its specific purpose.

- 1 The SuperHyway system interconnect facilitates the integration of several different types of sub-systems. It is used for closely coupled subsystems which have stringent memory latency/bandwidth requirements.

- 2 The PCI bus provides a standard interface which is used to expand the capabilities of the Eval chip and Reference board to provide a variety of product demonstrators.

- 3 The SuperHyway socket is an expansion port which supports the rapid integration of application modules without changing the eval chip core.

#### 1.1.1 Address map

The CPU accesses a single 32-bit flat address space in which all of the external memory and device register are accessible. The entire address space is accessible from all memory requesters. *Table 3 on page 22* illustrates the memory map.

#### 1.1.2 Interrupt architecture

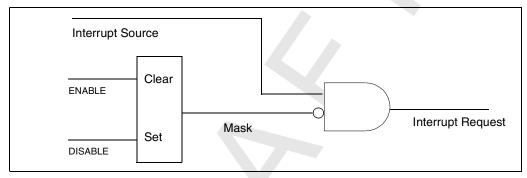

The system uses a conventional interrupt architecture. A programmable interrupt controller INTC which is responsible for multiplexing and filtering interrupt requests onto the **irq** and **nmi** lines of the CPU. The INTC implements priority and route interrupts.

#### 1.1.3 DMA architecture

A multiple channel DMA controller permits autonomous data transfers along multiple channels.

#### 1.2 Debug architecture

SH-5 has a dedicated high-speed debug interface to connect the target system to a development host. This is independent of the JTAG interface and is capable of operating at clock speeds of up to 100 MHz.

The CPU core has eight watchpoints: four instruction address, two memory write<sup>1</sup>, two instruction opcode. Each watchpoint has a control register field which defines the action when a hit occurs. Possible actions include:

- sending a trace packet to the debug link for writing into external debug adapter memory,

- writing the trace packet into an area of target system memory,

- generating a CPU debug trap which invokes a monitor program,

- incrementing a performance counter,

- generating a pulse on a TRIGGER\_OUT pin.

All actions except CPU debug trap are non-intrusive.

The CPU core also supports branch trace and fast printf functions which send trace packets to the debug link for writing into external debug adapter memory.

The SuperHyway bus has a bus analyzer for monitoring selected bus transactions. The bus analyzer has watchpoints, a trace buffer and control register fields which define the action when a hit occurs. Possible actions are the same as for CPU watchpoints.

The debug link operates as a reduced speed extension to the SuperHyway bus with both bus master and bus slave capability. By using the bus slave capability, the CPU (or any other bus master) can access memory in an external debug adapter simply by using the appropriate address range. This allows the CPU, or any other bus master, to fetch boot code instructions over the debug link or write to data memory in the external debug adapter.

$<sup>1. \ \</sup> Future\ implementation\ may\ include\ 2\ memory\ read\ watchpoints.$

By using the SuperHyway bus master capability of the debug link, debug software running on a development host can access the whole SuperHyway address space, including all watchpoint control registers, without involving the CPU. Special memory-mapped registers allow debug software running on a development host to directly control the CPU using suspend, resume, change reset vector, soft reset commands.

The debug link supports several different price/performance options for connecting to a development host. At the simplest, a \$50 signal converter connects to the parallel port of a personal computer but does not support real-time tracing. A higher performance option requires an external debug adapter containing SRAM, for use as the trace buffer, plus a processor for managing the debug link protocol.

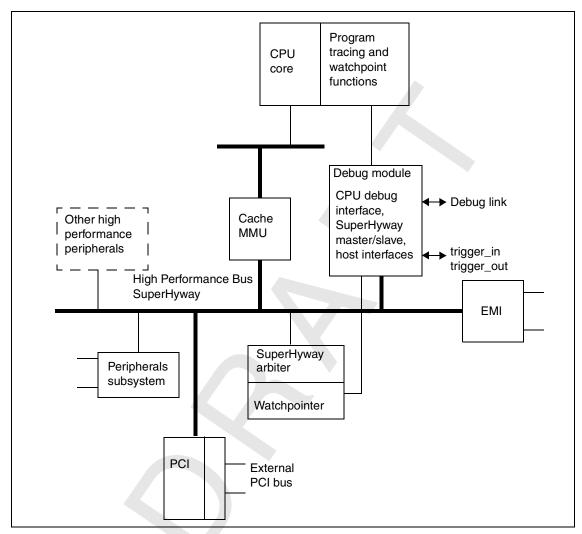

This architecture is illustrated in *Figure 2*.

Figure 2: SH-5 debug architecture

## 2

## System organization

#### 2.1 Introduction

The SH-5 system architecture is modular. An SH-5 implementation consists of a number of modules which communicate using one or more interconnects. The interconnect to which the CPU core is connected provides the main path to external memory. This interconnect provides a memory-mapped packet routing mechanism between modules. It is known as the SuperHyway and forms the backplane of highly integrated systems which use the SH-5. The SuperHyway specifies a protocol which defines how packets are represented and propagated. The name SuperHyway is given to the family of implementations of this protocol on SH-5 chips.

A typical SH-5 implementation is a single chip which contains one or more CPU cores, one or more product-specific SH-5 modules, an interconnect, a peripheral subsystem, an external memory interface and a module dedicated to supporting debug of the core and system.

#### 2.2 SuperHyway architecture

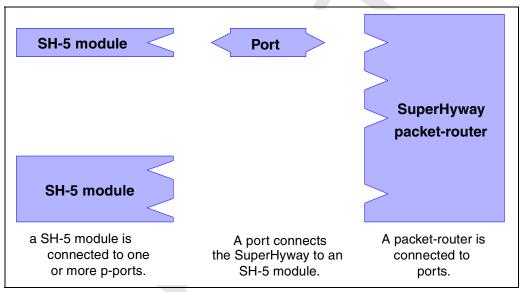

The SuperHyway architecture provides the 'glue' that binds together a set of SH-5 modules. A connection between the SuperHyway and an SH-5 module is called a port (sometimes referred to as a p-port). A SuperHyway port supports a bi-directional flow of packets between the interconnect and an SH-5 module.

The distinction between the SuperHyway architecture and implementation is important. This section, *SuperHyway architecture*, defines the abstractions that are used to build implementations containing a SuperHyway interconnect. The architecture includes an abstract view of the packets, the SuperHyway, the port, a SH-5 module and the protocol.

The implementation determines how the SuperHyway, the ports and the required modules are physically represented. It also defines how many SH-5 modules are implemented and how these are connected to the SuperHyway.

In all SH-5 systems there is at least one interconnect path and at least one SH-5 module. Each SH-5 module is connected to the SuperHyway using at least one port. The SuperHyway provides complete connectivity between SH-5 modules.

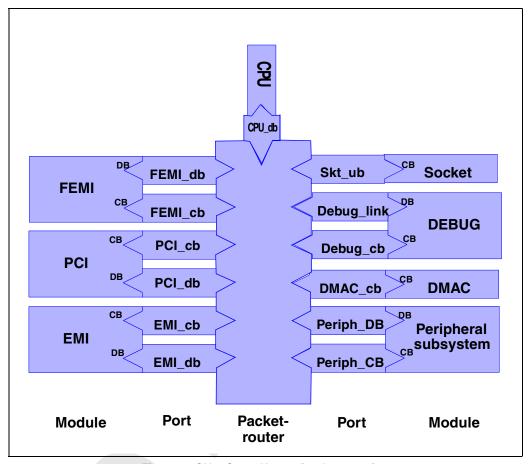

The architectural relationship between the SuperHyway packet-router, the port and the SH-5 module is illustrated in *Figure 3*.

Figure 3: SuperHyway packet-router, port and SH-5 module architecture

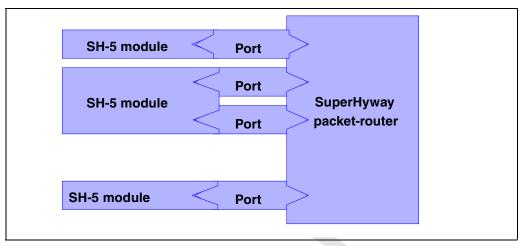

A simple implementation containing a packet-router, two single-ported SH-5 modules and one double-ported SH-5 module is illustrated in *Figure 4*.

Figure 4: A simple implementation

The SH-5 eval chip implementation of the SuperHyway packet-router architecture is described in *Section 2.5*: *SH-5 SuperHyway implementation on page 22*.

#### 2.2.1 Packets

The packet is the unit of data transfer through the SuperHyway. Communication between SH-5 modules is achieved by the exchange of packets between those SH-5 modules.

A packet is composed of fields. Each field has a number of possible values to characterize that packet. Every packet contains a destination field which is used to determine which SH-5 module the packet should be routed to. Further information on packets is given in *Section 2.2.6*: *SuperHyway protocol on page 16*. In particular, packets contain a field that indicates the type of access made by that packet.

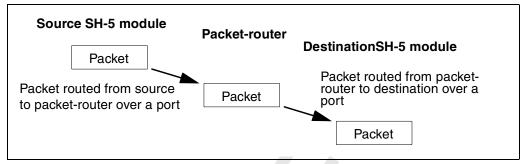

Each packet journey is associated with a source SH-5 module and a destination SH-5 module. The source sends a packet over a port into the packet-router. The packet-router arranges for the packet to be routed to a port connected to the destination. The destination then receives this packet over that port from the packet-router. It is possible for the source and destination to be the same SH-5 module.

A packet route from a source to a destination is illustrated in *Figure 5*. In packet routing diagrams, such as *Figure 5*, the vertical direction represents time with time flowing forward down the page.

Figure 5: A packet route

#### 2.2.2 Transactions

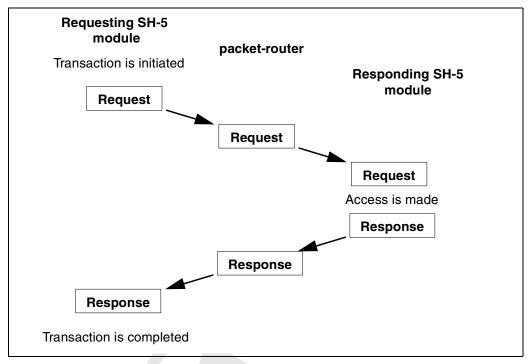

A transaction is an exchange of packets that allows an SH-5 module to access the state of another module using the SuperHyway protocol. A transaction consists of the transfer of a request packet from a requesting module to a responding module, followed by the transfer of a response packet from that responding module back to the requesting module. The request packet initiates the transaction and its contents determine the access to be made. The response packet completes the transaction and its contents indicate the result of the access.

This style of communication is called split phase. The separation between the request packet and the response packet allows systems to be constructed which are tolerant of high latency SH-5 modules. A requesting module can send multiple requests into the SuperHyway packet-router before any responses are received. This is called request pipe-lining and allows the latencies of those transactions to be overlapped.

There is a causal relationship between a request packet and its corresponding response packet since the request packet must be received before the response packet can be sent. Additionally, there is a one-to-one correspondence between request packets and response packets.

When a response packet is received by the SH-5 module that sent the corresponding request, the transaction is complete. It is guaranteed that the access associated with the response has been committed to by the destination module. This means that, apart from internal latency inside the destination module, the access is completed as viewed through all ports to that module. Any subsequent requests to that destination module will therefore act after that access.

This guarantee means that time-ordering of accesses at a destination can be imposed by waiting for the corresponding response.

A response packet also indicates whether the request was valid or not. The response packet is called an ordinary response if the request was valid, or an error response if the request was invalid.

The following sections elaborate on the actions comprising a single transaction.

#### Request

A request packet is constructed by a requesting SH-5 module when that module needs to make an access to a particular target module. This target module is recorded in the request packet's destination or address field. The requesting module is the source of the request packet and sends that packet into the packet-router. The packet-router arranges for that request packet to be routed from its source to its destination. The destination receives the request packet from the packet-router and services that access according to the information in the received request packet. The destination is known as the responding module because it replies to the request packet using a response packet.

#### Response

A response packet is constructed by a responding module in order to reply to a previous request. The module that originated that request packet is recorded in the response packet's destination field. The responding module is the source of the response packet and sends that packet into the packet-router. The packet-router arranges for that response packet to be routed from its source to its destination. The destination receives the response packet from the packet-router and matches that response to the original request in order to complete the transaction.

#### A complete transaction

A packet routing diagram showing a complete transaction is given in *Figure 6*.

Figure 6: A SuperHyway transaction

#### 2.2.3 Packet-router

The packet-router provides a packet routing interconnect for communication between SH-5 modules. The packet-router arranges for packets to be routed from their source module to their destination module. A variety of packet-router implementations are possible. Implementations include, but are not limited to, a bus, a crossbar and a packet routing network.

All packets passed into the packet-router contain a destination field which is used to route the packet. The packet-router contains a mapping from all possible destination field values to an appropriate p-port. The mechanism by which this mapping is established and the mapping itself are defined by a packet-router implementation.

The packet-router needs to interpret only a few fields of a packet. It must inspect the destination field to route the packet. The bulk of the packet does not need to be interpreted by the routing mechanism and is used to convey information between the requesting module and the responding module.

#### 2.2.4 SuperHyway ports

A port provides bi-directional packet-level communication between the packet-router and an SH-5 module. A module may have multiple port connections to the packet-router. Multiple ports may be used to increase the bandwidth between a module and the packet-router. Multiple ports may also be used to decouple logically separate functional units within that module.

#### 2.2.5 SH-5 modules

SH-5 modules (abbreviated to modules) communicate using packets routed via the packet-router. The interpretation placed on packets of different types by an SH-5 module depends on the implementation of that module.

Example modules include a CPU, a memory or a device. A CPU module will typically generate request packets to fetch instructions and to access data. A memory module will typically service request packets and generate response packets to return the results of those memory accesses. An example device module might service request packets and generate response packets to access the memory-mapped state of the device. It might also have a DMA engine to allow the device to access memory by generating request packets.

#### 2.2.6 SuperHyway protocol

The protocol is a memory-mapped packet routing protocol.

#### **Packet routing**

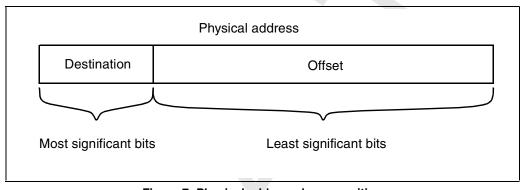

Packets are associated with a physical address. A physical address is an unsigned integral value that indicates a location in physical memory. Physical memory is byte-addressed.

Physical addresses are split into two parts as illustrated in *Figure 7*.

Figure 7: Physical address decomposition

The most significant bits of a physical address identify the destination to which a packet is to be sent. The least significant bits of a physical address are an offset that identifies a location within that destination. The offset information is present in request packets to identify the location at which the request is targeted. The offset information is not present in response packets.

The size of a physical address, the number of destination bits and the number of offset bits are defined by the implementation. The packet-router is arranged so that every packet-router access is associated with a single destination.

The packet-router uses the destination field to perform routing. Each possible destination field value is uniquely associated with a p-port and hence is uniquely associated with a module (the module connected to that p-port). When the packet-router routes a packet, it inspects the destination field, determines the appropriate p-port, and routes the packet to that p-port and hence onto the destination module.

A particular module may be able to handle requests for multiple destination fields. Multiple different destination field values may map to the same p-port. It is common for memory modules to handle requests for a contiguous range of destination field values. This allows a memory module to provide a physical address space, larger than that possible with a single destination field value, which is viewed as contiguous physical memory when addressed by the p-protocol.

#### **Packet classification**

A packet has a class and a type.

A packet's class is either a request packet or a response packet. The response packet class is subdivided into two different kinds of response packet: ordinary response packets and error response packets. The term 'response packet' refers to either an ordinary response packet or an error response packet, unless the surrounding context makes it clear that a particular kind of response packet is intended.

A packet's type indicates the memory transaction associated with that packet. The SH-5 implementation uses four basic kinds of memory operation: **read**, **write**, atomic **read-modify-write** and **cache-coherency** operations.

These are shown in the table below:

|                          | Transaction name | Request parameters <sup>a</sup>            | Response<br>parameters |

|--------------------------|------------------|--------------------------------------------|------------------------|

| Memory read              | Load8            | addr <sub>8</sub> , byte-mask              | word <sup>b</sup>      |

|                          | Load16           | addr <sub>16</sub>                         | 2 words                |

|                          | Load32           | addr <sub>32</sub>                         | 4 words                |

| Memory write             | Store8           | addr <sub>8</sub> , byte-mask, word        | -                      |

|                          | Store16          | addr <sub>16</sub> , byte-mask,<br>2 words | -                      |

|                          | Store32          | addr <sub>32</sub> , byte-mask,<br>4 words | -                      |

| Atomic read-modify-write | Swap8            | addr <sub>8</sub> , byte-mask, word        | word                   |

Table 2: SH-5 p-router transactions

|                 | Transaction name | Request parameters <sup>a</sup>          | Response<br>parameters |

|-----------------|------------------|------------------------------------------|------------------------|

| Cache coherency | Flush            | dest <sup>c</sup> , addr <sub>32</sub> , | -                      |

|                 | Purge            | dest <sup>c</sup> , addr <sub>32</sub>   | -                      |

Table 2: SH-5 p-router transactions

- a. addr<sub>n</sub> is used to denote an n-byte aligned address.

- b. A word in the SH-5 system corresponds to eight bytes.

- The dest field here is the port identifier of the cache controller. The address is a 32-bit address.

The packet class and packet type are combined to form a packet opcode.

#### **Memory transaction descriptions**

The transactions supported by the p-protocol are described below. In this description a word is 8 bytes of memory.

The **Load8** transaction reads up to 8 bytes of data from an 8-byte aligned location in a destination. The transaction is qualified by an 8-bit mask; each bit of this mask indicates whether a particular byte in the location is to be accessed or not. If all 8 bytes of data are read then it is a whole-word transaction. If less than 8 bytes of data are read then it is a subword transaction.

The **Load16** transaction reads 16 bytes of data from a 16-byte aligned location in a destination.

The **Load32** transaction reads 32 bytes of data from a 32-byte aligned location in a destination. The requestor may indicate which word within the four words being accessed should be returned first to implement critical word first fetches.

The **Store8** transaction writes up to 8 bytes of data to an 8-byte aligned location in a destination. The transaction is qualified by an 8-bit mask; each bit of this mask indicates whether a particular byte in the location is to be accessed or not. If all 8 bytes of data are written then it is a whole-word transaction. If less than 8 bytes of data are written then it is a subword transaction.

The **Store16** transaction writes 16 bytes of data to a 16-byte aligned location in a destination. This is qualified by a 16-bit mask.

The **Store32** transaction writes 32 bytes of data to a 32-byte aligned location in a destination. This is qualified by a 32-bit mask.

The **Swap8** transaction allows up to 8-bytes of data to be read from and then the same quantity of data written to a word location in memory. The read and write are performed atomically. The transaction is qualified by an 8-bit mask. Each bit of the mask indicates whether a particular byte is to be accessed or not. The data is word aligned.

Cache coherency transactions are described in *Section 2.3*.

#### 2.3 Cache coherency support

Cache coherency transactions are provided primarily to support the integration of the PCI bridge into the system. However the coherency support is general and can be used by any modules attached to the system interconnect.

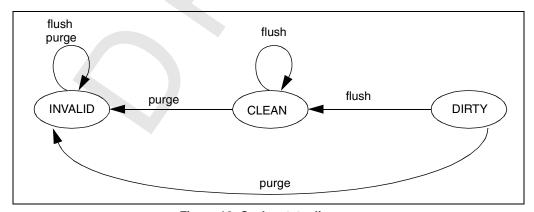

There are two cache control transactions: **Flush** and **Purge**. They are defined in the following sections.

#### 2.3.1 Flush

The flush transaction has a single operand which is the physical address to be flushed from the cache:

Flush <physical address>

When a flush transaction is received from the interconnect, by the CPU cache controller, it causes the cache controller to lookup the address in the cache. If the lookup yields a miss, or a hit to a line which is unmodified with regard to main memory, then the cache controller will issue a response to the flush request immediately following the lookup. If the lookup yields a hit to a line which is modified with regard to main memory then the cache controller causes a writeback of the line to main memory. Following the writeback the cache controller issues a response to the flush request.

Responses to flush requests are simple acknowledgments; they do not carry any data.

The <physical address> should be 32-bit aligned. The low order 2 bits, if not zero, are ignored.

#### 2.3.2 **Purge**

The purge transaction has a single operand which is the physical address which is to be purged from the cache:

Purge <physical address>

When a purge transaction is received from the interconnect, by the CPU cache controller, it causes the cache controller to lookup the address in the cache. If the lookup yields a miss, then the cache controller will issue a response to the flush request immediately, following the lookup. If the lookup yields a hit then the cache controller causes a writeback of the line to main memory (if the line has been modified in the cache) and then invalidates the line. Following the invalidation the cache controller issues a response to the flush request.

Responses to purge requests are simple acknowledgments; they do not carry any data.

The <physical address> should be 32-bit aligned. The low order 2 bits, if not zero, are ignored.

#### 2.3.3 Coherency maintenance

The use of flush and purge by a module in association with appropriate cache behavior provides a level of cache coherency. In particular it guarantees two properties:

- 1 That a read operation by module to an address in shared system memory will receive the value last written to that address. The time of the access is given as the time at which the flush is received by the cache controller. The module read operation is guaranteed to get a data value coherent with the value of system memory no earlier than the time of access.

- 2 That a write operation by a module to an address in shared system memory will be completed such that the data written is readable by all memory users after the time of access. The time of access is given as the time at which the write operation is performed to system memory following the purge of the data cache(s).

See Chapter 3: SH-5 CPU on page 53 for details of cache controller behavior.

Other features 21

#### 2.3.4 Use of coherency transactions

When a module wishes to make a coherent request to shared memory, the module performs the following routine:

1 Splits the memory request into a number of non-cache-line straddling system interconnect requests.

For each of these requests it does the following:

- 2 For a read a flush request is sent to the data cache port, for a write a purge request is sent to the data cache port.

- 3 The module waits until it receives a response from the cache controller.

- 4 For a read, a load request is then sent to the main memory. For a write, a store request is sent to main memory.

- 5 The memory's response indicates the completion of the coherent access.

#### 2.4 Other features

The SH-5 SuperHyway implementation also contains a number of additional features to enhance the system functionality. This includes support for module powerdown, module freeze and visibility of transaction traffic.

#### 2.4.1 Module powerdown

The SH-5 supports partial and complete system powerdown by stopping clocks to various parts of the system. This is achieved under software control by accesses to the clock, power and reset controller (CPRC) logic. Once a module powerdown request has been received, the SuperHyway ensures requests to that module are responded to with an error response, so that no further new requests are routed to that module. This keeps the system live, and allows it to be debugged. Details may be found in *Chapter 10: Clock, power and reset controller on page 259*.

#### 2.4.2 Debug features

#### Module freeze

To aid in system analysis or control over critical execution areas, the SH-5 supports a module freeze mechanism. The SuperHyway, under debug module control, is able to isolate a module from the system by stopping that module generating any new requests to the system. This may be used to simplify the system behavior when the user has specific requirements. Details may be found in *Volume 3 Debug, Chapter 3 External Debug Interfaces*.

#### **Transaction tracing**

In the SH-5 SuperHyway, all traffic is made visible to a bus analyzer associated with the debug module. This is able to log or capture any traffic across the SuperHyway<sup>1</sup>. To reduce the amount of traffic captured, the triggering event may be based on one or more of the following; address range, opcode, source identity, transaction identity. Details may be found in *Volume 3 Debug, Chapter 3 External Debug Interfaces*.

#### 2.5 SH-5 SuperHyway implementation

SH-5 modules share a common physical address space for memory. The SuperHyway provides point-to-point connectivity between all SH-5 modules based on this address map.

The SH-5 eval chip contains several direct ports. One of these are CPU's and the remainder support external memory, peripherals, debug and peripherals. The modules which are directly connected to the packet-router are shown below. Some SH-5 modules may have more than one connection to the packet router. The full list of p-modules and p-ports for SH-5 is given in *Table 3*.

| SH-5 module P-ports name  | P-port name (abbreviation) |

|---------------------------|----------------------------|

| Peripheral subsystem      | PERIPH                     |

| Debug Module              | DEBUG                      |

| External Memory Interface | EMI                        |

Table 3: SH-5 modules and p-ports

1. Subject to bandwidth limitations.

| Flash ROM interface         | FEMI   |

|-----------------------------|--------|

| CPU core                    | CPU    |

| PCI Interface               | PCI    |

| DMA controller              | DMAC   |

| SuperHyway expansion Socket | SOCKET |

Table 3: SH-5 modules and p-ports

### 2.5.1 Supported transactions

SH-5 designs support the following transaction types

**Load8** - read 8 bytes (1 \* 64 bit word)

**Load16** - read 16 bytes (2 \* 64 bit word)

**Load32** - read 32 bytes (4 \* 64 bit words)

**Store8** - write 8 bytes (1\* 64 bit word)

**Store16** - write 16 bytes (2\* 64 bit word)

Store32 - write 32 bytes (4 \* 64 bit words)

**Swap8** - swap 8 bytes (1\*64 bit word)

Flush (address)

Purge (address)

#### 2.5.2 Implementation

All transactions on the SH-5 eval chip are implemented on a non-multiplexed 64-bit interface. Each transaction is constructed from a request packet and a response packet. Each packet is constructed from a series of cells or tokens framed using an EOP (end of packet) signal. These cells are defined by the SH-5 SuperHyway interface.

Each request cell can carry the following information:

```

ADDRESS[31:3]

OPCODE[7:0]

MSK[7:0]

SRC[7:0]

TID[7:0]

DATA[63:0]

```

If a request packet contains more information than a single cell may hold, it is constructed from a sequence of cells framed using EOP.

Each response packet carries the following information:

```

R_OPCODE[7:0]

R_SRC[7:0]

R_TID[7:0]

R_DATA[63:0]

```

Again if the response packet contains more information than a single cell, it is constructed from a sequences of cells framed using the R\_EOP signal.

## 2.5.3 Data organization

For simple memory accesses (load or store) the MSK field indicates the bytes involved in the transaction. Other bytes are invalid. The relationship between the target ADDRESS, MSK and DATA fields is as follows:

Each transaction has a defined ADDRESS[31:3] which specifies an aligned 64-bit quadword. For operations transferring a quadword or less, the MSK field validates the data lanes and specifies which bytes are to be accessed.

The important aspect to understand is that the SuperHyway byte lanes are labelled by the significance of the byte carried within a quadword. The significance of the data carried is invariant in little and big endian modes but the address which a particular physical byte lane is associated with depends on whether the system is in little or big endian mode. For example, in little endian mode the byte lane of lowest significance always corresponds to a byte having an address 8n. This same byte lane (that is, the least significant) in big endian mode corresponds to a byte having an address 8n+7.

For accesses larger than a quadword, data is transferred as a sequence of quadwords starting at the addressed quadword and incrementing by a quadword until the number of quadwords indicated by the transaction opcode have been transferred. The increment will wrap around if the addressed quadword is not aligned to the size of the transfer. So that, for example, for a 32-byte load request whose (byte) address is 8 the sequence of transfers will be the quadwords at (byte) addresses 8, 16, 24 and finally 0.

This is described further in Section 2.8: SH-5 endianess and data mapping on page 43.

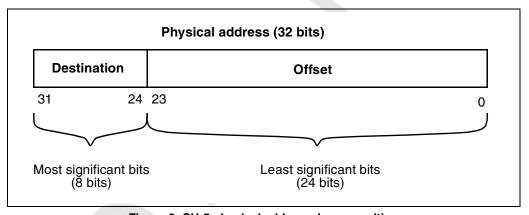

#### 2.5.4 SH-5 physical memory organization

An SH-5 physical address is 32 bits wide. The eight most significant bits of this physical address identify a destination. The 24 least significant bits of this physical address are an offset that identifies a location within that destination. This is illustrated in *Figure 8*.

Figure 8: SH-5 physical address decomposition

The  $2^{24}$  bytes of address space associated with a particular destination is called a memory block (MB). There are 256 memory blocks in the SH-5 physical address space and each memory block is 16 Mbytes in size.

There are three types of memory block: control blocks (CB), data blocks (DB) and undefined blocks (UB). These blocks are described in *Section 2.7.1: Memory blocks on page 29*.

# 2.6 SH-5 physical address map

Each memory block is associated with a particular p-port and hence with a particular module. The mapping from memory blocks to p-ports is not programmable on SH-5. The mapping defines the SH-5 physical address map and is given in  $Table\ 4$ .

| P-port<br>acronym<br>(or RESERVED) | Block<br>type | Destination range | Physical address range    | Physical<br>address<br>space |

|------------------------------------|---------------|-------------------|---------------------------|------------------------------|

| FEMI_db                            | DB            | 0x00 to 0x07      | 0x00000000 to 0x07FFFFF   | 128 Mbyte                    |

| FEMI_cb                            | СВ            | 0x08              | 0x08000000 to 0x08FFFFF   | 16 Mbyte                     |

| PERIPHERAL_cb                      | СВ            | 0x09 to 0x0A      | 0x09000000 to 0x0AFFFFF   | 32 Mbyte                     |

| Debug_link                         | DB            | 0x0B              | 0x0B0000000 to 0x0BFFFFFF | 16 Mbyte                     |

| Debug_cb                           | СВ            | 0x0C              | 0x0C000000 to 0x0CFFFFF   | 16 Mbyte                     |

| CPU                                | СВ            | 0x0D              | 0x0D0000000 to 0x0DFFFFFF | 16 Mbyte                     |

| DMAC                               | СВ            | 0x0E              | 0x0E000000 to 0x0EFFFFF   | 16 Mbyte                     |

| RESERVED                           | UB            | 0x0F to 0x3F      | 0x0F000000 to 0x3FFFFFF   | 784 Mbyte                    |

| PCI_db                             | DB            | 0x40-0x5F         | 0x40000000 to 0x5FFFFFF   | 512 Mbyte                    |

| PCI_cb                             | СВ            | 0x60              | 0x60000000 to 0x60FFFFF   | 16 Mbyte                     |

| RESERVED                           | UB            | 0x61 to 0x6F      | 0x61000000 to 0x6FFFFFF   | 240 Mbyte                    |

| SHwy Socket                        | UB            | 0x70 to 0x7F      | 0x70000000 to 0x7FFFFFF   | 256 Mbyte                    |

| EMI_DRAM                           | DB            | 0x80 to 0xFE      | 0x80000000 to 0xFEFFFFFF  | 2032 Mbyte                   |

| EMI_cb                             | СВ            | 0xFF              | 0xFF000000 to 0xFFFFFFF   | 16 Mbyte                     |

Table 4: SH-5 physical address map

The physical address map is organized so that each p-port deals with a contiguous range of blocks and with a set of blocks of the same type. The only exception to this organization is the treatment of accesses to undefined blocks. All accesses to undefined blocks are routed to the Debug\_cb p-port where they are handled as errors.

The SH-5 packet-router implementation is illustrated in *Figure 9*.

Figure 9: SH-5 SuperHyway implementation

| 0:     | xFF00 0000 |                                      |           |            |

|--------|------------|--------------------------------------|-----------|------------|

|        |            | EMI                                  |           |            |

|        |            | High performance                     | DRAM      |            |

| 0:     | x8000 0000 |                                      |           |            |

| 0:     | x7F00 0000 |                                      |           |            |

|        |            | Reserved                             |           |            |

| 0:     | x6100 0000 |                                      |           |            |

| 0:     | x6000 0000 |                                      |           |            |

|        |            | PCI                                  |           |            |

|        |            |                                      |           |            |

| 0:     | x4000 0000 |                                      |           |            |

|        |            |                                      |           |            |

|        |            | Reserved                             |           |            |

| O      | x0F00 0000 |                                      |           |            |

| 0:     | x0E00 0000 | <br>DMAC                             |           |            |

| 0:     | x0D00 0000 | <br>CPU                              |           |            |

| 0:     | x0C00 0000 |                                      |           |            |

| 02     | x0B00 0000 | DEBUG                                |           |            |

| I      |            | Peripheral subsy                     | /stem     |            |

|        |            | (Timers, clocks, serial              |           |            |

| 0      | x0900 0000 | rupt controller, power ment controll |           |            |

| 0:     | x0800 0000 |                                      | <u> </u>  |            |

| -<br>I |            | FEMI                                 |           |            |

|        |            | (FLASH,SRAM,ROM,                     | MPX, com- |            |

| 0:     | x0000 0000 | panion chip inter                    |           |            |

|        |            |                                      |           |            |

|        | Γ          | Control Registers                    |           | Data Space |

|        | L          | _                                    |           | •          |

Table 5: SH-5 eval chip physical address map

#### 2.6.1 SH-5 debug link

The SH-5's debug module provides features for debugging the system. It interacts with the debug facilities in the CPU, to provide, among other things tracing, and bus monitors. A principal debug support takes the form of the debug link. The debug link uses SH-5 pins to implement a bit-serial communication port which is typically used to connect the SH-5 to a host development system (abbreviated to host).

The debug link protocol contains packet formats that allow the host to engage in transactions with SH-5 modules. There are debug link packets that correspond to packet-router request packets and response packets of each packet-router transaction. This allows the host to access the SH-5's physical address space via the packet-router. Additionally, the SH-5 can engage in transactions with the host by making accesses to a memory block that maps onto the debug link.

These are powerful features which can be used, for example, to:

- boot-strap the SH-5 through memory provided by the host,

- support interactive or post-mortem debugging of the SH-5,

- provide host-based input and output facilities to software running on the SH-5.

# 2.7 SH-5 conventions

The SH-5 follows additional conventions which present a consistent interface to SH-5 modules.

## 2.7.1 Memory blocks

There are three types of memory block: control blocks (CB), data blocks (DB) and undefined blocks (UB).

A control block contains a collection of memory-mapped registers holding a variety of status and control information for an SH-5 module. There is a one-to-one association between SH-5 modules and control blocks. All control blocks contain a Version Control Register (VCR). A VCR identifies the module associated with that control block, the version number of that module, the memory blocks associated with that module (if any) and the module's error status.

A data block is a contiguous range of data memory blocks associated with a module. These blocks are not control blocks and do not contain a VCR. Data blocks are typically used to provide access to memory. A module may be associated with zero, one or more data blocks. The set of data blocks associated with a module must be contiguous in physical address space. Each data block is associated with exactly one module.

All blocks which are neither control blocks nor data blocks are undefined blocks. Undefined blocks do not provide useful functionality and all accesses to undefined blocks are errors. Packets destined for an undefined block are routed to the Debug module where an error is recorded.

### 2.7.2 Control registers

A control register is a memory-mapped register held in a control block. Control registers are 64-bit wide and allocated on addresses that are 8-byte aligned.

Each control register has a unique name. Control register names are composed hierarchically by concatenating subnames, separated by a period ('.'), together. The left-most subname indicates the module that implements that control register. Succeeding subnames repeatedly refine the classification of the control register. A control register can be refined to a field by concatenating the control register name with the field name separated by a period ('.'). A field can be refined to a single bit by concatenating the field with the bit name separated by a period ('.').

An example control register is DEBUG.VCR. This name refers to the VCR register within the DEBUG module. An example field is DEBUG.VCR.PERR\_FLAGS. This name refers to the PERR\_FLAGS field within the DEBUG.VCR control register. An example bit is DEBUG.VCR.PERR\_FLAGS.ERR\_RCV. This name refers to the ERR\_RCV bit within the DEBUG.VCR.PERR FLAGS field.

Control registers are accessed using the p-protocol. The set of transactions that are supported by a control register depends on the implementation of that control register. Control registers are typically read using a whole-word **LoadWord** transaction and written using a whole-word **StoreWord** transaction. It is possible to have control registers that support other transactions, though these are much less common.

Each control block is fully populated by an array of control registers. For SH-5 there are 2<sup>21</sup> control registers in each control block. Typically, however, each module will only implement a very small proportion of the available control registers.

The semantics of a control register are, in general, specific to that control register and defined by the architecture of the module that implements that control register.

However, there are conventions which all control registers adhere to. Additionally, there is a standard table format for describing the layout of control registers. These are described in the following sections.

Note: Each SH-5 CPU contains a control block and debug control registers which are memory mapped and so can be accessed from the debug link.

#### **Register conventions**

Each control register is one of 'reserved', 'undefined' or 'defined'.

#### 'RESERVED' control registers

'reserved' control registers are used to reserve parts of the control block address space. A read from a 'reserved' control register always returns zero. Writes to a 'reserved' control register are always ignored.

If a control register is 'reserved', it is possible that this control register will have a different implementation in future components in the SH-5 family.

#### 'Undefined' control registers

'undefined' control registers are used to identify parts of the control block address space where the behavior of accesses is not well defined by the architecture. The specification of a particular 'undefined' control register may elaborate on the actual behavior.

Typically, an access causing a request to an 'undefined' control register will result in an error flag being set in the VCR of the module that deals with the request. Additionally, a response from an access to an 'undefined' control register might result in an error flag being set in the VCR of the module that deals with the response.

A read from an 'undefined' control register will typically return an undefined value or an implementation defined value. A write to an 'undefined' control register will typically be ignored or lead to behavior that is architecturally undefined.

If a control register is 'undefined', it is possible that this control register will have a different implementation in future components in the SH-5 family.

#### 'Defined' control registers

'Defined' control registers are implemented and the behavior of accesses is well defined. A 'defined' control register is composed of one or more fields. Each field is a collection of bits in the control register. All bits in a 'defined' control register belong to a field. Further categorization of a 'defined' control register is performed at the field level.

#### **Field conventions**

Each field in a 'defined' control register is one of 'reserved' or 'defined'.

#### 'RESERVED' fields

'Reserved' fields are used to reserve parts of a control register. A read from a 'reserved' field always returns zero. Writes to a 'reserved' field are always ignored.

If a field is 'reserved', it is possible that this control field will have a different implementation in future components in the SH-5 family.

#### 'Defined' fields

A 'defined' field is one of 'read-only', 'read-write' or 'other'.

A 'read-only' field indicates that the value of the field cannot be changed by software. A read from a 'read-only' field returns the value associated with that field. A write to a 'read-only' field is ignored.

A 'read-only' field indicates that the value of the field has conventional read and write behavior. A read from a 'read-write' field returns the value of that field. A write to a 'read-write' field sets the value of the field.

An 'other' field indicates that the field has atypical semantics. The specification of an 'other' field describes the actual semantics.

In addition to the above defined field types, a field is also either volatile or non-volatile. A non-volatile field is never changed autonomously by hardware, while a volatile field may be changed autonomously by hardware. When a field is volatile, its specification describes the actual semantics. A non-volatile 'read-only' field has an immutable value.

When the value of a field is not architecturally defined, the field is said to have an undefined value. For example, a writable field might have an undefined value between hard reset and the first time that it is written.

A field may have some values which are reserved. These values must not be written into that field, otherwise the behavior of the access is not well defined by the architecture. The specification of a particular writable field which has reserved values will enumerate the reserved values and may elaborate on the actual behavior. It is possible that all values apart from one specific value may be reserved. In this case, the field must be programmed with that specific value.

#### **Control register layout**

The standard table format for describing the layout of a control register is illustrated in *Table 6*.

| REGISTER |           |         |            | OFFSET     |      |  |  |  |

|----------|-----------|---------|------------|------------|------|--|--|--|

| Field    | Bits      | Size    | Volatile?  | Synopsis   | Туре |  |  |  |

| FIELD    | Bits      | Size    | Volatile   | Synopsis   | Туре |  |  |  |

|          | Operation |         | Operation  |            |      |  |  |  |

|          | When      | read    | Read       |            |      |  |  |  |

|          | When      | written | Write      |            |      |  |  |  |

|          | HARD      | reset   | Hard_reset | Hard_reset |      |  |  |  |

Table 6: Standard table format for describing a control register layout

The capitalized fields in this table are place-holders for the following information:

- Register the name of the register.

- Offset the byte-offset of the register in the control block of the module containing the register.

- Field the name of the field.

- Bits the bit numbers occupied by this field. The least significant bit in a control register is bit 0; the most significant bit in a control register is bit 63. A single number indicates a single bit. The notation [x:y] represents the inclusive contiguous range of bits starting at bit x and ending at bit y.

- Size the number of bits occupied by this field.

- Volatile a 'V' symbol indicates that the field is volatile, while '-' indicates that the field is not volatile.

- Synopsis a summary of the purpose of this field.

- Type the type of this field. This can be 'RES' to indicate a 'reserved' field, 'RO' to indicate a 'read-only' field, 'RW' to indicate a 'read-write' field or 'other' to indicate an 'other' field.

- Operation defines the operation of this field.

- Read defines the behavior of this field for a valid read access.

- Write defines the behavior of this field for a valid write access.

- Hard\_reset defines the value of this field after a hard reset.

The set of rows used to describe a field are repeated for each field in the control register.

### 2.7.3 Version control registers

The control register at offset 0 of every control block is the version control register of the module that implements that control block. Thus, the physical address of a control block is the same as the physical address of the VCR in that control block.

Every VCR uses the same layout. This allows software to parse a VCR value without knowledge of the implementation of the module that provided the VCR. It is architecturally guaranteed that no VCR will ever have a value of zero.

The VCR of each module contains the following fields:

- PERR\_FLAGS contains the packet error flags (p-error flags) which report the error status of the interface between this module and the packet-router. The set of supported flags and their standard semantics are described in *Section* 2.7.4: P-error flags on page 37. Further information on the supported p-error flags of the module is given in the VCR description for that module.

- MERR\_FLAGS contains module specific error flags (m-error flags). The set of supported flags (if any) and their semantics are given in the VCR description for that module.

- MOD\_VERS is provided to allow software to distinguish different versions of a module. This allows software to take appropriate action if there are differences between module versions.

- MOD\_ID is provided to allow software to identify and distinguish different modules.

- BOT MB indicates the number of data blocks associated with this module.

• TOP\_MB - if there is one or more data blocks associated with this module then TOP\_MB is the number of control blocks associated with the module. If there are no data blocks associated with this module then TOP\_MB is the offset of the last block associated with this module.

If a module is associated with data blocks, then these data blocks will be contiguous in the address space. This allows ranges of data blocks to be described as the inclusive range from the value of BOT\_MB to the value of TOP\_MB.

The VCR format is illustrated in *Table 7*.

| MODULE.VCR |           |      |                                        | 0x000000                                                     |        |  |  |

|------------|-----------|------|----------------------------------------|--------------------------------------------------------------|--------|--|--|

| Field      | Bits      | Size | Volatile?                              | Volatile? Synopsis                                           |        |  |  |

| PERR_FLAGS | [7:0]     | 8    | 1                                      | P-port error flags                                           | Varies |  |  |

|            | Operation | 1    | See Section                            | on 2.7.4: P-error flags on page 37                           |        |  |  |

|            | When rea  | ad   | See Section                            | on 2.7.4: P-error flags on page 37                           |        |  |  |

|            | When wr   | tten | See Section                            | on 2.7.4: P-error flags on page 37                           |        |  |  |

|            | HARD re   | set  | 0                                      |                                                              | _      |  |  |

| MERR_FLAGS | [15:8]    | 8    | <b>Y</b>                               | <ul> <li>✓ P-module error flags (module specific)</li> </ul> |        |  |  |

|            | Operation | 1    | See Section                            | on 2.7.5: M-error flags on page 41                           |        |  |  |

|            | When rea  | ıd   | See Section                            | tion 2.7.5: M-error flags on page 41                         |        |  |  |

|            | When wri  | tten | See Section                            | See Section 2.7.5: M-error flags on page 41                  |        |  |  |

|            | HARD re   | set  | 0                                      |                                                              |        |  |  |

| MOD_VERS   | [31:16]   | 16   | _                                      | Module version                                               | RO     |  |  |

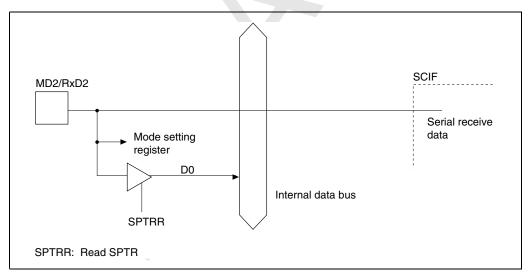

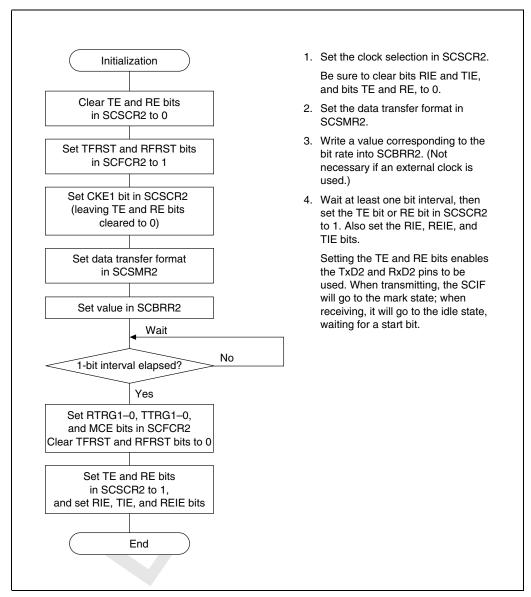

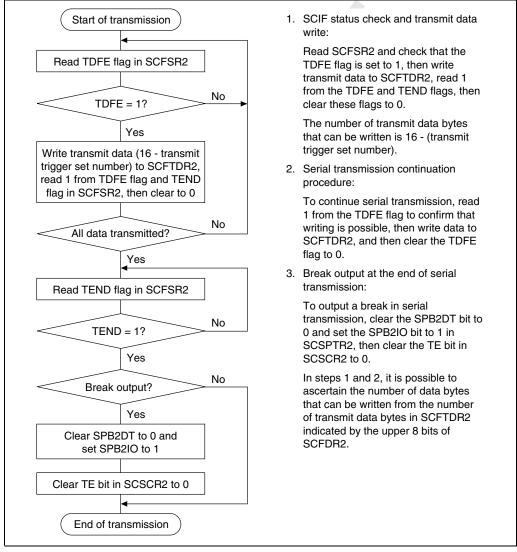

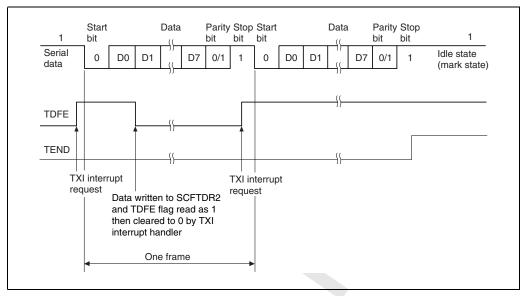

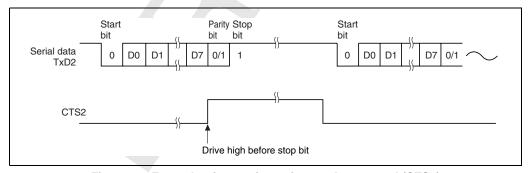

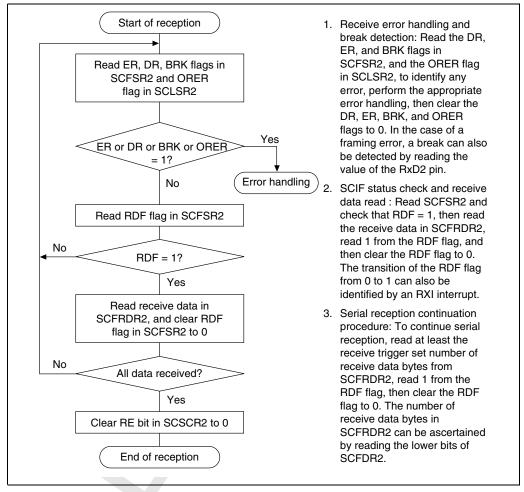

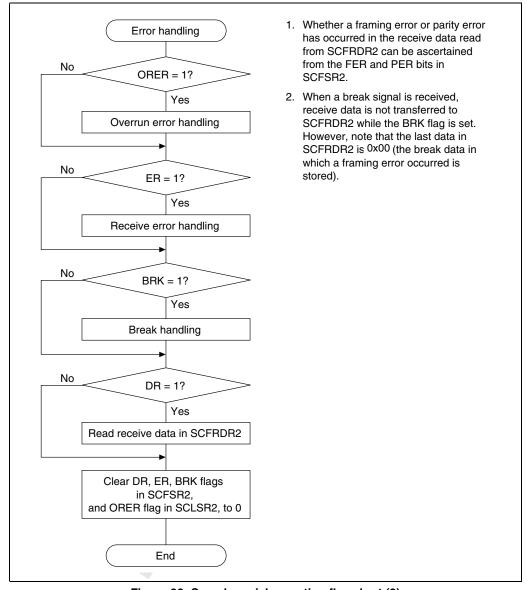

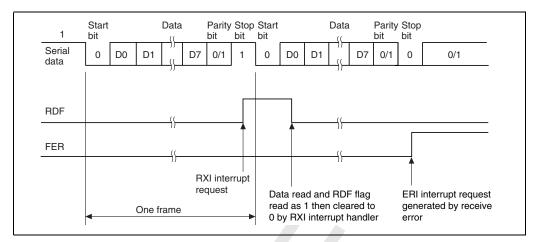

|            | Operation | 1    | Used to indicate module version number |                                                              |        |  |  |